# A Partitioning Scheme to Guarantee Minimum Execution Time for Multiple Applications in Sensor Network Nodes

Daehoon Kim Dept. of Computer Engineering Kyung Hee University Yongin 446-701, Korea gogohhcom@khu.ac.kr BeomSeok Kim Dept. of Computer Engineering Kyung Hee University Yongin 446-701, Korea Passion0822@khu.ac.kr Jinsung Cho Dept. of Computer Engineering Kyung Hee University Yongin 446-701, Korea chojs@khu.ac.kr

Abstract—Due to rapid development of embedded system technologies, miniaturization of low-power sensor nodes becomes possible. Based on these improvements of sensor nodes, several sensor applications can run on a single sensor hardware and all of the applications in sensor network should be guaranteed the real-time requirements and independence. To satisfy these requirements, the virtualization concept was proposed. However, the virtualization cannot be applied to sensor nodes because it requires powerful computing resources. To solve this problem, the partitioning scheme which is categorized into temporal partitioning and spatial partitioning has been proposed. In this paper, we design and implement temporal partitioning scheme for sensor nodes and validate that our implementation guarantees minimum execution time of each partition.

Keywords—Sensor network; Virtualization; Partitioning; Scheduling; Threads

## I. INTRODUCTION

In last few years, embedded system is dramatically developed and it is used in various areas such as airplane, air conditioner, television, and sensors. Especially, development of sensor devices makes it possible that sensor network is used in various area such as military, u-healthcare, and monitoring system.

In general, a single application runs on a single hardware because sensor nodes have limited hardware resources. In recent years, however, sensor devices are developed rapidly and it makes possible that various applications run on a single sensor device. Based on these improvements of sensor nodes, many sensor applications can run on a single sensor hardware, and all the sensor applications should provide the reliability and independence at the same time. For example, airplane system should operate properly because the whole airplane system may cause serious problems if one of applications makes error.

To guarantee these requirements, the virtualization scheme has been proposed. The virtualization supports various OS (Operating System) on each virtual machine in a single hardware. However, the virtualization scheme requires powerful computing resources. As mentioned above, sensor nodes have limited resources and it is not suitable that we directly apply virtual machine to sensor nodes. To handle this problem, the partitioning scheme has been proposed. The partitioning scheme consists of two parts: temporal partitioning and spatial partitioning [1]. Temporal partitioning divides the time resources of all applications and guarantee the minimum execution time. Contrastively, spatial partitioning divides physical memory of applications and it protects memory space of each application using memory protection of CPU. While the partitioning scheme is similar to concept of virtualization, it requires lower hardware resources than virtualization. However, existing spatial partitioning is difficult to adapt to sensor nodes because most CPUs on sensor nodes does not support memory protection.

In this paper, we design the partitioning architecture that guarantee minimum execution time using temporal partitioning with a limited performance of hardware and implement the partitioning on KHIX using ATmega128.

The rest of the paper is organized as follows: Section 2 discusses background and existing studies of partitioning scheme. In Section 3, we describe the architecture of partitioning and its performance is evaluated via implementation in Section 4. Finally, Section 5 concludes this paper.

## II. BACKGROUND

## A. Virtualization

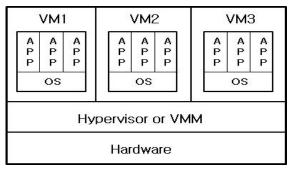

Virtualization provides independence of each virtual machine. Figure 1 illustrates concept of virtualization. The virtualization can be categorized into two schemes: fullvirtualization and para-virtualization. Full-virtualization has several virtual machines which have different guest OS that does not need to modify. It should be provided virtualization function of CPU. Therefore, guest OS requests to control the hardware to CPU and the CPU delivers the request to hypervisor which can control the hardware. The strength of full-virtualization is that guest OS does not need to change. On the other hand, guest OS of para-virtualization requests to control the hardware to hypervisor directly. Therefore, paravirtualization which should modify its guest OSs can provide higher performance than full-virtualization. Meanwhile, these virtualization schemes are available on hardware based on excellent performance.

Fig. 1. Concept of virtualization

## B. Partitioning

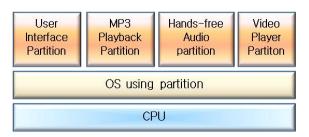

While partitioning scheme is similar to virtualization scheme, it provides independent spaces of several applications that are divided into each partition with lower computing resources than virtualization. Therefore, partitioning scheme is more suitable than virtualization to apply sensor network. Partitioning scheme can be categorized into two schemes: temporal partitioning and spatial partitioning. Spatial partitioning means that physical memory of one partition is not affected by the other partitions. On the other hand, temporal partitioning means that each process is allocated time resource to guarantee independence. Figure 2 represents the partitioning scheme. This partitioning scheme operates on a single hardware like as a lot of independent hardware. This scheme is used for embedded system such as car and airplane system based on ARINC 653 standard [2].

Fig. 2. Partitioning scheme

# C. ARINC 653

Avionics system consists of various kind of electronic systems that perform the different work. These electronic systems are integrated into IMA (Integrated Modular Avionics). IMA is performed on a single computing environment because electronic equipment is very heavy weight and variety. In this situation, reliability of each applications and independence are very important. To guarantee this problem, ARINC 653 standard that define the partitioning scheme in avionics system was proposed [2-4]. ARINC 653 standard was written not only partitioning scheme but also whole avionic systems.

# D. KHIX

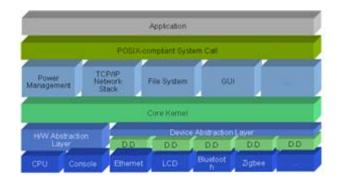

KHIX (OS developed by Kyung-Hee University) is the OS that can provide the extension and reconfiguration. And it is medical sensor OS providing API based on POSIX [5]. Embedded system of sensor network needs the composition which is suitable to purpose because of many limitations that are CPU performance, memory and consumption of electronic power. Figure 3 shows a block diagram of KHIX. Each function allows easy extension by making component and easy transplant the other process through HAL (Hardware Abstract Lager). Also it allows to develop the program which easily provides the API based on POSIX.

Fig. 3. Architecture of KHIX

## E. ATmega128

We design the partitioning scheme in the sensor network. Sensor network requires small capacity of hardware and highspeed microcontroller. The ATmega128 fulfills these requirements. The ATmega128 is manufactured by using ATmel's high-density nonvolatile memory and provide up to 16 MIPS throughput at 16MHz and on-chip 2-cycle multiplier. The device has UART0 and UART1 communication ports for serial communication under UART environment and uses USB ISP cable in order to download programs to the ATmega128 processor. The device has 128kbytes of Flash, 4kbytes SRAM. And it is supported with C compilers [6-7].

#### *F. Related works*

To provide performance of integrated system and reliability on sensor nodes, independence of each application that runs on a single hardware has become more important. For this reason, there exist studies to guarantee requirements of sensor nodes.

In recent years, study of vehicle mounted infotainment system which simultaneously operates multiple applications tries to apply virtualization and partitioning scheme to provide independence of each application that executes on a single vehicle. The authors of [8] proposed the partitioning scheme that consists of two non-virtual partitions and single virtual partition. They suggest the performance evaluation using various platforms that run on the each partition on a single hardware. In the result, they verify that overload of one partition does not affect the other partition.

COS (Core OS of DECOS project) has the partitioning scheme that consists of temporal partitioning and spatial partitioning [9]. Temporal partitioning has two-level scheduling. First level scheduling divides the several time slots and it allocate the partitions. When system is divided into several partitions, allocate the fixed scheduling with predefined weight. Second level scheduling that does dynamic scheduling with workload of each partition is event or event handler of each partition. Spatial partitioning is to provide memory protection through the MMU (Memory Management Unit) which control the CPU to access the memory. They propose this partitioning scheme that each partition uses the divided resources.

Temperature-aware partitioning embedded system was also proposed. High temperature negatively affects reliability as well the costs of cooling and packaging [10]. This system is divided into two partitions that consist of "cool" task and "hot" task. If "hot" tasks are executed consecutively, the system is negatively affected. Therefore, the system always checks the temperature of board. Then the partition scheduler dynamically determines the executing partition. Experimental results show that task partitioning algorithms can effectively reduce the peak temperature.

These studies assume that they developed with powerful computing resources. However, sensor nodes in sensor network have limited hardware resources and it cannot be applied existing partitioning schemes. To handle this problem, we design the partitioning scheme on the sensor OS which operates on sensor node with ATmega128 that has limited performance of hardware.

## III. DESIGN OF PARTITIONING ON KHIX

Since general purposed sensor nodes do not have capacity of memory protection, spatial partitioning cannot work on sensor nodes. Therefore, we design partitioning which provides only temporal partitioning based on pure software side. Proposed partitioning is developed on KHIX.

# A. Temporal partitioning

Temporal partitioning requires that it does not affect CPU usage (process resource) of each divided partition. In this paper, we design the independent scheduling scheme of each partition.

| Application 1                             |      |                                        | App 2                      |                             | Арр 3                        |  |  |  |

|-------------------------------------------|------|----------------------------------------|----------------------------|-----------------------------|------------------------------|--|--|--|

| Thread<br>1<br>Thread<br>3<br>Thread<br>5 |      | nread<br>2<br>nread<br>4<br>nread<br>6 | Thread<br>7<br>Thread<br>9 | Thread<br>8<br>Thread<br>10 | Thread<br>11<br>Thread<br>12 |  |  |  |

| Scheduler (Priority R.R Scheduler)        |      |                                        |                            |                             |                              |  |  |  |

| Thr1                                      | Thr2 | Thr5                                   | Thr7                       | Thr3                        | Thr4                         |  |  |  |

| Kernel                                    |      |                                        |                            |                             |                              |  |  |  |

Fig. 4. KHIX without temporal partitioning

As shown in Figure 4, KHIX system has various applications on a single node with non-temporal partitioning. Each application has several threads and they have different weight. KHIX system uses the priority-based RR (Round Robin) scheduler which fairly schedules by priority of threads. If a thread has the highest priority and many workloads, it may monopolize the usage of CPU. To solve this problem, we propose partitioning scheme that several threads in divided partition are performed independently. In addition, we design the temporal partitioning using integrated management partition scheduler to guarantee minimum execution time of each application.

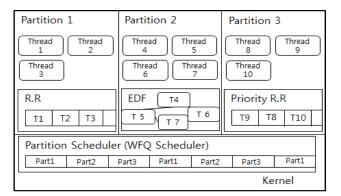

Figure 5 shows KHIX with proposed temporal partitioning and integrated management partition scheduler. Each partition has different scheduler and consists of several threads. Each partition is allocated the fixed weight by user, and the partition scheduler divides the time resources depending on weight of partition. By this design of proposed scheme, it can prevent monopoly of CPU and guarantee minimum execution time of each partition(application).

Fig. 5. KHIX with proposal temporal partitioning

## B. Partition

One partition consists of several threads. When system is started, the weight of each partition is allocated by user, and scheduling is decided with requirement of partition. Each partition doesn't affect to the other partition. therefore error of one partition doesn't affect the whole system. For example, Figure 5 shows KHIX with proposed temporal partitioning. In case of the partition 1, it uses RR scheduler which fairly allocates the time resources and partition 2 uses EDF (Earliest Deadline First) scheduler which needs to guarantee the dead line of the thread in real time. Scheduler of partition 3 is priority-based RR as mention above. These schedulers are executed independently.

## C. Partition scheduler

Kernel has partition scheduler which schedules partitions and each partition has its own scheduler. Partition scheduler uses the WFQ (Weight Fair Queue) scheduler that guarantees the execution time with weight of partition. It is similar to RR scheduler which fairly divides the execution time of threads. However, it allocates different time resources to each partition based on weight of partition and it is a scheduler adaptable to dynamic environment. In addition, it can provide prevention of CPU monopoly, guarantee of independence and minimum execution time of each partition. This partition scheduler cannot be applied to hard real time sensor network because this scheme guarantees minimum execution time of all threads, therefore this scheme is hard to provide deadline of all threads.

## IV. IMPLEMENTATION

#### A. Implementation on ATmega128

Fig. 6. Zigbex-II node with ATmega128

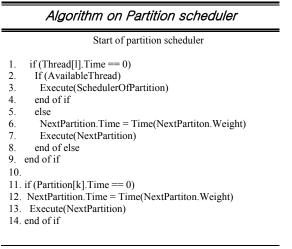

We implemented proposed temporal partitioning scheme using partition scheduler. Figure 6 shows Zigbex- II node which is infrastructure to develop proposed scheme based on ATmega128. At the start of the system, the partition scheduler and each scheduler initializes variables and registers alarm signal which is periodically called every 10ms. After system initialization time, partition scheduler allocates the time resources to each partition based on weight of partition. Each partition executes its member threads by using its own scheduler. When alarm signal is called, time resource of thread and partition is decreased. Scheduler of partition tries to find available thread in executing partition when time of thread become 0 and time of partition is more than 0. If it finds the available thread, it loads thread to CPU. Otherwise, partition scheduler change to next partition and allocates the time resources using weight of partition. If any partition is not available, CPU executes the idle thread. Figure 7 shows scheduling algorithm of proposed partitioning scheme.

Fig. 7. Pseudo code of Partition scheduler.

## B. Validation of partitioning

We perform experiment which verifies the guaranteeing minimum execution time using temporal partitioning. The experiment was proceeded during 1sec (1000ms) and time quantum of OS is 20ms. Detail environment of experiment is shown in Table 1.

In experiment, five threads have different priority such as High, Middle, and Low. These priorities and usage of CPU can be modified by users, and we set the data as shown Table I. We compare the performance of KHIX with proposed scheme with KHIX with priority-based RR scheduler. The experiment validates that guarantee the minimum execution time when error occur.

| Application<br>(Partition)     | Thread<br>No. | Priority of<br>thread | CPU usage<br>(weight) |  |

|--------------------------------|---------------|-----------------------|-----------------------|--|

| Application 1                  | Thread 1      | High                  | 30 %                  |  |

| (Partition 1)                  | Thread 2      | Low                   |                       |  |

| Application 2                  | Thread 3      | Middle                | 30 %                  |  |

| (Partition 2)                  | Thread 4      | High                  |                       |  |

| Application 3<br>(Partition 3) | Thread 5      | Low                   | 20 %                  |  |

TABLE I. Experiment environment

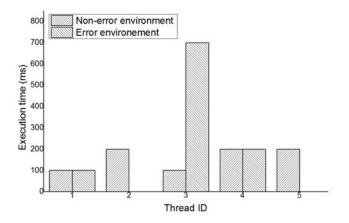

Figure 8 is results of experiment on KHIX using priority RR. All threads take the time resources of 80% usage of CPU. We assume that the thread 3 occurs the infinite loop error and the thread 1 and the thread 4 have higher priority than thread 3. Therefore, the thread 1 and 4 do not affected by error of the threads 3. However, the thread 2 and the thread 5 have lower priority than the thread 3. It cause problem with minimum execution time of threads because infinite loop error always make state of thread 3 'Ready' or 'Execute'. As the result, threads which have lower priority than the thread 3 cannot guarantee the minimum execution time.

Fig. 8. Execution time of threads using priority R.R

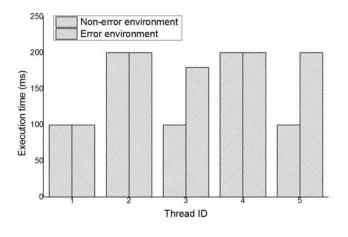

Fig. 9. Execution time of threads using partitioning

Figure 9 illustrates result of execution time on KHIX with proposed temporal partitioning scheme. As shown the result of non-error environment, all threads are fairly distributed. Meanwhile, thread 2 and thread 5 which have lower priority than thread 3 are guaranteed the minimum execution time when thread 3 occurs error. The thread 3 executes during about 180ms which is longer than thread 3 of non-error environment because the thread 3 additionally use 20% of CPU resource when thread 3 has infinite loop error. As the result, proposed temporal partitioning scheme can guarantee the minimum execution time of each thread.

#### C. Efficiency of partition scheduler

The partitioning scheme is developed on the KHIX system. In sensor network which has limited resources of sensor nodes, code size is very important. The size of KHIX system using priority-based RR scheduler is 2,057 bytes which takes 50.2% of SRAM and 5,498 bytes which takes 4.2% of flash memory. Similarly, the size of KHIX system with proposed temporal partitioning scheme is 2,390 bytes which takes 58.3% of SRAM and 7,918 bytes which takes 6.0% of flash memory. This result means that the proposed temporal partitioning scheme has capacity of multi-application execution and it is useful to apply sensor network to real world.

#### V. CONCLUSION

In this paper, we propose the temporal partitioning scheme to prevent the CPU monopoly, guarantee of independence and minimum execution time of each partition. To validate performance of proposed scheme, we also implement proposed scheme on ATmega128 board and measure execution time of each thread. Results of experiment shows that proposed scheme can guarantee minimum execution time of all thread in the system. Moreover, system which is applied proposed scheme has low capacity and it can be used in general purposed sensor nodes. As a result, proposed partitioning system is suitable to sensor network in real world.

## REFERENCES

- B. Leiner, M. Schlager, R. Obermaisser, and B. Huber, "A Comparison of Partitioning Operating System for Integrated Systems," *In Proc of SAFECOMP*, pp. 342-355, 2007.

- [2] S. H.VanderLeest, "ARINC 653 HYPERVISOR," In Proc of Digital Avionics Systems Conference, pp. 5.E.2-1 – 5.E.2-20, 2010

- [3] S. Han, H. Jin, "Virtualization-based ARINC 653 Partitioning for Avionics Software," In Proc of KCC, 2011

- [4] S. Han, H. Jin, "Kernel-Level ARINC 653 Partitioning for Linux," In Proc of ACM Symposium on Applied Computing, pp. 1632-1637, 2012

- [5] Y. Baek, J. Cho "KHIX : A Scalable and Reconfigurable Embedded System Operating" in KCC, 2007

- [6] M. Kang, S. Chom, J. Kim, U. Chong, "Implementation of Non-Stringed Guitar Using ATMEGA128," In Proc of IFOST, pp. 585-588, Oct. 2007

- [7] X. K. Pham, D. Q. A. Vo, N. H. Nguyen, T. P. Cao, "PID-Neural Controller based on AVR Atmega 128," *In Proc of ICARCV*, pp 1573-1576, Dec. 2008.

- [8] S. Han, J. Seok, H. Jin, "A Partitioning Scheduling Scheme to Support Efficient Mixed Partitoning," *In Proc of KIISE*, 2013

- [9] J. Craveiro, J. Rufino, F. Singhoff "Architecture, Mechanisms and Scheduling Analysis Tool for Multicore Time-and Space-Partitioned Systems," In Proc of ACM SIGBED Review. Vol. 8, No. 3, pp 23-27, Sep. 2011

- [10] Z. Wang, S. Ranka, P. Mischra, "Temperature-aware Task Partitioning for Real-Time Scheduling in Embedded Systems,", *In Proc of VLSID*, DOI = 10.1109/VLSID.2012.64